GLOBAL JOURNAL OF RESEARCHES IN ENGINEERING ELECTRICAL AND ELECTRONICS ENGINEERING Volume 12 Issue 9 Version 1.0 Year 2012 Type: Double Blind Peer Reviewed International Research Journal Publisher: Global Journals Inc. (USA) Online ISSN: 2249-4596 & Print ISSN: 0975-5861

# Area Optimized High Throughput IDMWT/DMWT Processor for OFDM on Virtex-5 FPGA

# By Anitha.K, Dr.Dharmistan.K.Varugheese & Dr N.J.R.Muniraj

Aarunai engg college/anna university

*Abstract* - OFDM is one of the most popular modulation techniques that is been widely used in most of the wireless and wired communication links. The OFDM architecture consists of QAM modulator and orthogonal frequency modulator. In this work we propose DMWT based orthogonal frequency modulator for achieving higher BER. The IDMWT architecture is designed considering N=4, thus the preprocessing unit converts the QAM samples of N to 2N and is modulated using DMWT filters. The filtered output is further transmitted and is received at the receiver. During the post processing, N samples are extracted by use of DMWT demodulation technique. The complex architecture of IDMWT and DMWT are reduced for its complexity and speed by the modified architecture. The DMWT architecture is modified for FPGA implementation improving the area, power and speed performances. The modified DMWT architecture is implemented on VirtexII pro FPGA which operates at 300MHz frequency and occupies area of less than 1%, with power consumption less than 28mW. The proposed design is suitable for real time and low power applications.

GJRE-F Classification : FOR Code: 090601

# AREA OPTIMIZEDHIGHTHROUGHPUTIDMWTDMWTPROCESSORFOROFDMONVIRTEX-SFPGA

Strictly as per the compliance and regulations of:

© 2012. Anitha.K, Dr.Dharmistan.K.Varugheese & Dr N.J.R.Muniraj. This is a research/review paper, distributed under the terms of the Creative Commons Attribution-Noncommercial 3.0 Unported License http://creativecommons.org/licenses/by-nc/3.0/), permitting all non commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

# Area Optimized High Throughput IDMWT/DMWT Processor for OFDM on Virtex-5 FPGA

Anitha. $K^{\alpha}$ , Dr.Dharmistan.K.Varugheese<sup> $\sigma$ </sup> & Dr N.J.R.Muniraj<sup> $\rho$ </sup>

Abstract - OFDM is one of the most popular modulation techniques that is been widely used in most of the wireless and wired communication links. The OFDM architecture consists of QAM modulator and orthogonal frequency modulator. In this work we propose DMWT based orthogonal frequency modulator for achieving higher BER. The IDMWT architecture is designed considering N=4, thus the preprocessing unit converts the QAM samples of N to 2N and is modulated using DMWT filters. The filtered output is further transmitted and is received at the receiver. During the post processing, N samples are extracted by use of DMWT demodulation technique. The complex architecture of IDMWT and DMWT are reduced for its complexity and speed by the modified architecture. The DMWT architecture is modified for FPGA implementation improving the area, power and speed performances. The modified DMWT architecture is implemented on VirtexII pro FPGA which operates at 300MHz frequency and occupies area of less than 1%, with power consumption less than 28mW. The proposed design is suitable for real time and low power applications.

## I. INTRODUCTION

he FFT based OFDM uses complex exponential bases function to reduce interference hence it was replaced with wavelets to produce better performance at the cost of loss in orthogonality between the carriers [1] [2]. Mutiwavelets preserves high frequency components and also increases sensitivity better than scalar wavelets [7]. Multiwavelets show the perfect union of symmetry, orthogonally, finitely support and smoothness [8]. The design of orthogonal symmetric prefilter banks is shown with the discrete multiwavelet transform for image coding and digital communications. The new DMWT structure increases computational complexity, energy compaction ratio as well as the compression performance when applying to а VQ based image coding system[9][10]. А biorthogonal multi-wavelets filter has many characteristics, such as symmetry, compact support, orthogonality and 3-order vanishing moment[11].

The Fourier based OFDM (FFT-OFDM) use the complex exponential bases functions and it's replaced

by an orthonormal wavelets in order to reduce the level of interference. It is found that OFDM based on Haarbased orthonormal wavelets (DWT-OFDM) are capable of reducing the inter symbol interference ISI and inter carrier interference ICI, which are caused by the loss in orthogonality between the carriers [1] [2].

To further improve the performance gains a new transform is implemented based on Multifilters called Multiwavelets (DMWT-OFDM). These filters shows more properties which is not achievable in other transforms (Fourier and wavelet) [3].

A most important Multiwavelets filter is the GHM filter proposed by Geronimo, Hardian, and Massopust The Multiwavelets functions coefficients are 2X2 matrices ,and they must multiply vectors instead of scalars during transformation step. Thus multifilter bank requires 2 input rows. To start the analysis algorithm and to reduce the noise effects , the preprocessing step associates given scalar input signal of length N to a sequence of length-2 vectors[4] [5].

## II. PROPOSED SYSTEM FOR DMWT- OFDM

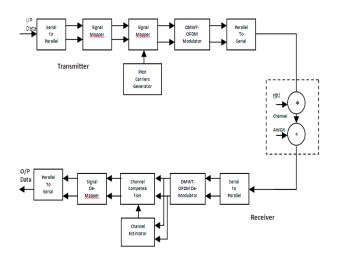

The block diagram of the proposed system for OFDM is depicted in figure (1).

Figure 1 : Block Diagram of DMWT-OFDM System

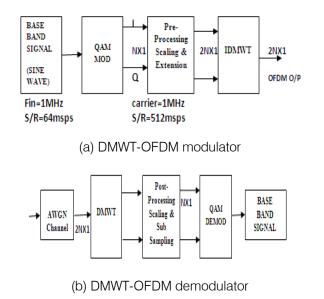

The OFDM modulator and demodulator of DMWT-based OFDM are shown in figure (2).

201

Author α : Assistant Professor, Arunai Engineering College, Tiruvannamalai Tamilnadu, India.

Author σ : Professor, Karpagam Engineering College, Coimbatore Tamilnadu, India.

Author **p** : Professor, Karpagam Engineering College, Coimbatore Tamilnadu, India.

#### Figure 2 : DMWT-OFDM modem system

The S/P converter, the signal demapper and the insertion of training sequence are same as in DWT-OFDM. After that, a computation of IDMWT for 1-D signal is achieved by using an over-sampled scheme of preprocessing (repeated row), the IDMWT matrix is doubled in dimension compared with that of the input, which is a square matrix of NxN, where N is in power of 2. Transformation matrix dimensions is equal to input signal dimensions after preprocessing. To compute a single-level 1-D discrete multiwavelets transform, the next steps are:

- 1. Checking input dimensions: With input vector of length N, where N is in power of 2.

- Constructing a transformation matrix *W* as in 3, using GHM low and high pass filters matrices given in 1 and 2, after substituting GHM matrix filter coefficients values, a 2NX2N transformation matrix results.

|     | $\int H_0$ | $H_1$ | $H_2$ | $H_3$ | 0       | 0     |   | 0     | 0     | 0        | 0     |   |    |

|-----|------------|-------|-------|-------|---------|-------|---|-------|-------|----------|-------|---|----|

|     | 0          | 0     | $H_0$ | $H_1$ | $H_{2}$ | $H_3$ |   | 0     | 0     | 0        | 0     |   |    |

|     | :          | ÷     | ÷     | ÷     | ÷       | ÷     | ÷ | ÷     | ÷     | ÷        | ÷     |   |    |

|     | $H_2$      | $H_3$ | 0     | 0     | 0       | 0     |   | 0     | 0     | $H_0$    | $H_1$ |   |    |

| W = | $G_0$      | $G_1$ | $G_2$ | $G_3$ | 0       | 0     |   | 0     | 0     | 0        | 0     |   | (3 |

|     | 0          | 0     | $G_0$ | $G_1$ | $G_2$   | $G_3$ |   | 0     | 0     | 0        | 0     | ۱ |    |

|     | :          | ÷     | ÷     | :     | :       | ÷     |   | :     | :     | ÷        | :     |   |    |

|     | 0          | 0     | 0     | 0     | 0       | 0     |   | $G_0$ | $G_1$ | $G_2$    | $G_3$ |   |    |

|     | $G_2$      | $G_3$ | 0     | 0     | 0       | 0     |   | 0     | 0     | $G_{_0}$ | $G_1$ |   |    |

3. Preprocessing the input signal by repeating the input stream with the same stream multiplied by a

constant  $\alpha$  , for GHM system functions  $\alpha = 1/\sqrt{2}$  .

4. Transformation of input vector which can be done by apply matrix multiplication to the 2NX2N constructed transformation matrix by the 2NX1 preprocessing input vector.

#### III. SOFTWARE REFERENCE MODEL RESULTS

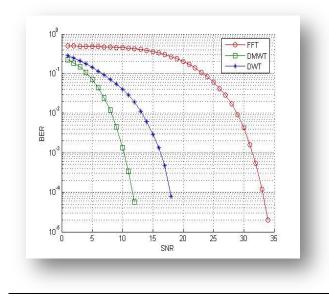

In this section the simulation of the proposed DMWT-OFDM system in MATLAB version 7 are achieved. And the bit error rate (BER) performance of the OFDM system considered in different channel models, the additive white Gaussian noise (AWGN) channel, the flat fading channel, and the selective fading channel [6].

#### a) Performance of dmwt-ofdm in awgn channel

In this section, the result of the simulation for the proposed DMWT-OFDM system is calculated and shown in figure (3), which give the BER performance of DMWT-OFDM in AWGN channel. It is shown clearly that the DMWT-OFDM is much better than the two previous system FFT-OFDM and DWT-OFDM. This is a reflection to the fact that the orthogonal bases of the multiwavelets is much significant than the orthogonal bases used in FFT-OFDM and DWT-OFDM.

© 2012 Global Journals Inc. (US)

*Figure 3 :* BER performance of DMWT-OFDM in AWGN channel model.

In this work, design and FPGA implementation of a hardware efficient DMWT architecture is carried out. The QAM modulated data which generates the I and Q channel signals are preprocessed and is modulated using IDMWT, the OFDM modulated data is transmitted through AWGN channel and is demodulated using DMWT, the base band signal is extracted using QAM demodulation. Figure 2 shows the detailed block diagram of OFDM modulation and demodulation. The input signal is considered as 1MHz signal with sampling frequency of 64Msps, the QAM modulator carrier frequency is chosen to be 64 MHz, the QAM symbols are obtained at 512Msps. The OFDM modulator has to process the modulated data at the rate of 512Msps. From the previous discussions, it is found that prior to OFDM modulation, the input samples are to be scaled and extended as 2N x 1 vector, which is the requirement for GHM based IDMWT. In order to achieve this the pre processing unit performs the scaling and extension operation, thus the incoming samples to preprocessing that are at 512Msps are preprocessed to 2N x1 with

#### IV. DESIGN OF DMWT/IDMWT ARCHITECTURE

1024 Msps. The preprocessed data is to be processed using IDMWT, this has to operate at frequency greater than 1024Msps.

# V. Design Of Idmwt

In this work, we select N=4, thus the QAM symbols are grouped into frames of 4 samples and is preprocessed. With N=4, the preprocessing unit extends the samples to 8 with scaling. The scaled samples are to be processed in the IDMWT with GHM wavelets of size 2N x 2N, with N=8, the GHM filter size is 8 x 8. The GHM filter for N=4 is given in equation

|    | H0         | H1 | <i>H</i> 2 | H3 |  |

|----|------------|----|------------|----|--|

|    | <i>H</i> 2 | H3 | H4         | H1 |  |

| W= | G0         | G1 | <i>G</i> 2 | G3 |  |

|    | G2         | G3 | G0         | G1 |  |

As we perform inverse IDMWT, the GHM filter coefficients are:

|    | H0         | H2       | G0         | G2 |

|----|------------|----------|------------|----|

| W= | H1         | H3<br>H0 | G1         | G3 |

|    | <i>H</i> 2 | H0       | <i>G</i> 2 | G0 |

|    | <i>H</i> 3 | H1       | G3         | G1 |

Using the above equation, the preprocessed data is modulated to generate OFDM signal. The OFDM signal using GHM filter can be mathematically represented as:

# $[Y] = [W_T] X]$ [2NX1][2NX2N][2NX1]

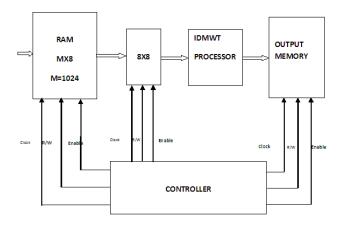

The above equation is implemented on FPGA. The input matrix is first stored in a memory of size Mx8, where M is an integer of size 1024. The input memory is loaded from the preprocessing unit. The controller reads the data from input memory into a intermediate memory of size 8x8, the controller also reads the corresponding GHM coefficients from memory. The input is multiplied and accumulated using dedicated multipliers on FPGA to compute the output samples. Figure below shows the top level block diagram of IDMWT logic for the I channel, which is similar for the Q channel.

## VI. COMPUTATION COMPLEXITY OF IDMWT

As the input is of size 8 x 1 and is 8 bit per sample, every input frame is multiplied by 2N rows of GHM filter coefficients. Thus it requires 2N\*2N multiplications and 2N(2N-1) additions. For computation of every output sample, ti requires 2N clock cycles (write 2012

data into intermediate memory) + 2N clocks for reading data from intermediate memory + 1 clock cycle for multiplication + 2N-1 clock for addition and another 2N clock cycle for write operation, thus for every output computation it requires 8N clock cycles. The latency is 8N clock cycles, throughput is 8N-1 clock cycles. In order to improve throughput and latency, it is required to modify the IDMWT architecture. In this work we propose a high speed DMWT and IDWMT architecture that is implemented on FPGA.

#### Modified DMWT architecture:

In the previous section the BER performance is analyzed and now the GHM matrix coefficients were calculated and substituted in equations 1, 2and 3 the equations 4 to 11 are derived to design multiwavelets. Here it is scaled with scaling factor 128. The table below shows co-efficient before and after scaling.

| Before  | After Scaling |

|---------|---------------|

| Scaling |               |

| 3/5√2   | 54            |

| 4/3     | 170           |

| 0.26819 | 34            |

| 0.1707  | 22            |

| 0.4145  | 53            |

| 0.7070  | 90            |

| 3/10    | 38            |

| 2/3     | 84            |

| 1/2     | 64            |

| 0.5207  | 66            |

| 0.08787 | 11            |

| 0.5207  | <b>6</b> 8    |

| 0.362   | 46            |

| 0.6864  | 88            |

| 0.3793  | 48            |

Table 1 : Scaled and Un scaled co-efficient

| Y0                         | 3/5/2                                                                                      | 4/3                                                    | -3/5√2                                  | 0                                     | 0                                     | 0                               | 0          | 0 ]  | X0                             |

|----------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------|---------------------------------------|---------------------------------------|---------------------------------|------------|------|--------------------------------|

| Y1                         | -1/20                                                                                      | -3/102                                                 | 9/20                                    | $1/\sqrt{2}$                          | 9/20                                  | -3/10/2                         | -1/20      | 0    | X1                             |

| Y2                         | 0                                                                                          | 0                                                      | 0                                       | 0                                     | 3/5/2                                 | 4/3                             | 3/5/2      | 0    | X2                             |

| <i>Y</i> 3                 | 9/20                                                                                       | -3/102                                                 | -1/20                                   | 0                                     | -1/20                                 | -3/102                          | 9/20       | 1/√2 | X3                             |

| <i>Y</i> 4                 | = -1/20                                                                                    | -3/102                                                 | 9/20                                    | -1/√2                                 | 9/20                                  | -3/102                          | -1/20      | 0    | $X0(1/\sqrt{2})$               |

| <i>Y</i> 5                 | -1/10/2                                                                                    | 3/10                                                   | 9/102                                   | 0                                     | 9/10/2                                | -3/10                           | -1/10/2    | 0    | $X1/\sqrt{2}$                  |

| <i>Y</i> 6                 | 9/20                                                                                       | -3/102                                                 | -1/20                                   | 0                                     | -1/20                                 | -3/102                          | 9/20       | -1/5 | $X^2/\sqrt{2}$                 |

| Y7                         | 9/102                                                                                      | -3/10                                                  | -1/10/2                                 | 0                                     | 1/10/2                                | -3/10                           | 9/102      | 0 ]  | $X3/\sqrt{2}$                  |

| y1<br>y2<br>y3<br>y4<br>y5 | $= (54)^{*}$ $= (34)^{*}$ $= (38)^{*}$ $= (53)^{*}$ $= (34)^{*}$ $= (66)^{*}$ $= (53)^{*}$ | fx0-22<br>fx0+8<br>fx0-22<br>fx0-22<br>fx0-22<br>fx0+1 | 2*x1+<br>4*x1<br>2*x1+<br>2*x1+<br>1*x1 | -53*;<br>+38<br>-34*;<br>-53*;<br>+68 | x2+9<br>*x2)<br>x2+6<br>x2-90<br>*x2) | 90*x3<br><br>64*x3<br>0*x3)<br> | )<br><br>) | (!   | (5)<br>(6)<br>(7)<br>(8)<br>9) |

#### a) Computation complexity of reduced equation

Equation above have been derived based on the modified GHM filter coefficients. From the above equations it is found that to compute every output sample, it is required to perform minimum of 3 multiplications and 2 additions. Thus for N=4, the number of multiplications and additions are 28 multiplications and 20 additions respectively. The number of multiplications and additions are reduced by more than 50%. This reduction in multiplication and addition optimizes the design in terms of area and power requirement. It is also found that the latency of the design is 8N clock cycles, but throughput is 7N clock cycles, which is faster compared with existing design which is 8N-1. The latency and throughput can be further improved with parallel and pipelining architecture.

## VII. Fpga Implementation Of Modified Dmwt/Idmwt

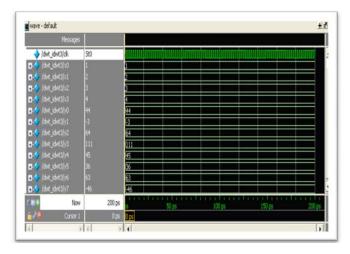

The HDL model for the modified equations of GHM filter is developed and simulated using ModeSim. Multiple test cases are chosen to test the functionality of the modified equation and is verified against software reference model results. The functionally correct HL code is synthesized using Xilinx ISE 10.1 targetting VirtexII pro FPGA. Next section discuss the results of FPGA implementation.

Figure 4 : Post Place and Route Simulation

It is seen that the pre-simulation and post place and route simulation results match, thereby proving that the design is perfectly mapped onto FPGA meeting the required design specifications.

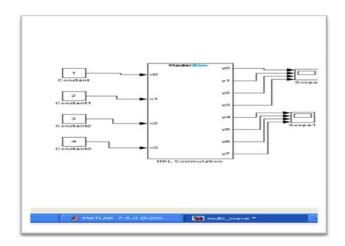

The HDL co simulation of the design is performed using matlab simulation which is shown in Figure5 below.

Figure 5 : HDL CO-Simulation

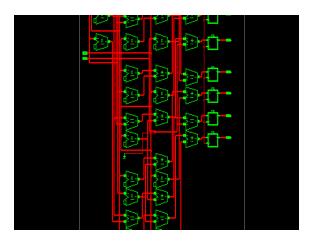

Figure 6 below shows the RTL schematic of the proposed design with interconnects between the various blocks. It is a technology independent schematic.

Figure 6 : RTL Schematic

a) Device utilization summary

| · · · · · · ·                |      |           |             |  |

|------------------------------|------|-----------|-------------|--|

| Logic Utilization            | Used | Available | Utilization |  |

| Number of 4 input<br>LUTs    | 126  | 27, 392   | 1%          |  |

| Number of<br>occupied Slices | 72   | 13, 696   | 1%          |  |

| Number of bonded<br>IOB'S    | 97   | 556       | 17%         |  |

| IOB Flip Flops               | 64   |           |             |  |

| Number of<br>MULT18X18s      | 18   | 136       | 13%         |  |

| Number of<br>BUFGMUXs        | 1    | 16        | 6%          |  |

#### b) Synthesis report

Target Device : xc2vp30-7-ff896

Minimum input arrival time before clock: 8.362ns Maximum output required time after clock: 3.293ns Total memory usage is 225952 kilobytes

# VIII. Conclusion

In this work, we propose a modified GHM filter architecture for OFDM modulation and demodulation. Software reference model for DMWT based OFDM model is developed and simulated to find the BER performances for various SNRs. The simulation results show that the DMWT OFDM model outperforms FFT and DWT based OFDM models. The DMWT coefficients that are fractions are converted to integers and are modified to reduce the number of multiplications and additions. The reduced GHM filter coefficients are used to process the QAM modulated data, thus reducing the computation complexity and making it suitable for FPGA implementation. The modified equations are modeled using HDL and implemented on FPGA VirtexII pro. The design operates at maximum frequency of 300MHz and consumes less than 1% resources and thus is suitable for real time applications. The design can be further improved for its latency and throughput by designing a parallel and pipelined architecture for DMWT/IDMWT.

## References Références Referencias

- Zhang H. et al, "Research of DFT-OFDM and DWT-OFDM on Different Transmission Scenarios.", Proceedings of the 2<sup>nd</sup> International Conference on Information Technology for Application (ICITA), 2004.

- Negash B.G. "Wavelet Based Multicarrier Transmission over Wireless Multipath Channels", MS.c Thesis, Delft University of Technology, Aug 2000.

- Cotronei M., et al, "Multiwavelet Analysis and Signal Processing", IEEE Transaction on Circuits and Systems II.

- 4. Strela, G. Strang et al, "The Application of Multiwavelet Filter Banks to Image Processing" IEEE Transaction on Image Processing, 1993.

- 5. Strela, "Multiwavelets: Theory and Application", Ph.D Thesis, MIT, June 1996.

- Biglieri E., Proakis J. and Shamai S. "Fading Channels: Information-Theoretic and Communications Aspects", IEEE Transactions on Information Theory, Vol. 44, No. 6, October 1998.

- Ragupathy, U.S.; Kumar, A. Senthil, "Investigation on mammographic image compression and analysis using multiwavelets and neural networks", International conference (ICoBE), 2012, Page(s): 17 - 21

- Liu Wei." An image coding method based on multiwavelet transform", Image and Signal Processing(CISP), 4<sup>th</sup> International Congress on Volume: 2 ,2011, Page(s): 607 – 610.

- 9. Tai-Chiu Hsung,Lun, D.P.-K., Ho, K.C, "Orthogonal symmetric prefilter banks for discreate wavelet transforms" Signal Processing letters, IEEE,Vol.13, 2006.

- Tai-Chiu Hsung; Lun, D.P.-K.; Yu-Hing Shum; Ho, K.C., "Generalised Discrete Multiwavelet Transform with Embedded Orthogonal Symmetric Prefilter Bank" Signal Processing, IEEE transaction ,Vol.55, 2007.

- Li Yongjun, Xu Xiaorong, "A Fractal Multi-Wavelet Filter Design And Application" Information Technology, computer engineering and management sciences (ICM), International Conference Volume: 2,2011, Page(s): 313 – 316.