Artificial Intelligence formulated this projection for compatibility purposes from the original article published at Global Journals. However, this technology is currently in beta. *Therefore, kindly ignore odd layouts, missed formulae, text, tables, or figures.*

# Robustness Evaluation Study of Power RF LDMOS Devices after Thermal Life Tests M. Masmoudi<sup>1</sup> <sup>1</sup> LATIS-ENISo, 4023 Sousse University, Tunisia *Received: 6 December 2016 Accepted: 2 January 2017 Published: 15 January 2017*

#### 7 Abstract

This paper presents a synthesis of robustness evaluation on power RF LDMOS devices and its 8 relation with electrical and physical behaviours after RF life-tests. It is important to 9 understand the physical degradation mechanism effects and the liaison on drifts of critical 10 electrical parameters after life ageing tests, in I-V such as threshold voltage (V th), the 11 feedback capacitance (C rss ) in C-V and the S-parameter (S 21) in RF. It shows with 12 tracking of set parameters that Hot Carrier Injection (HCI) phenomenon appears. It is the 13 main cause for device degradation leading to the interface state generation (traps), which 14 results in a build up of negative charge at Si/SiO 2 interface. More interface states are created 15 due to a located maximum impact ionization rate at the gate edge. Such simulations correctly 16 take into account interactions coupled between electrical, thermal and RF behaviours in 17 device inside using the FEM method. A numerical model (Silvaco-Atlas) was used to confirm 18 degradation phenomena. The problem of hot-electron should be taken into consideration in 19 the design of the power RF MOS devices and can be a useful tool to investigate reliability in 20 MOSFET. 21

22

23 Index terms—

## 24 1 Introduction

ateral diffused metal-oxide-semiconductor (LDMOS) have been widely used in many smart power applications. 25 Also on base stations, TV broadcast or in radar applications with high capabilities particularly in terms of RF, 26 output power and Power Added Efficiency (PAE). These applications can cause damage and limiting factors to 27 device reliability, especially to the gate oxide of MOS devices [1,2,3]. Quite often accelerated life tests of MOS 28 capacitors are performed by applying a high constant voltage at the gate contact (constant voltage stress: CVS) 29 or by injecting a constant current across the oxide (constant current stress: CCS) over a period of time. They 30 produce electrical instabilities which have been the subject of numerous experimental studies in MOS devices 31 [4,5]. Current is a more effective parameter than voltage for defect detection in MOSFET devices and CMOS 32 ICs, although both are necessary for complete testing. 33

34 Problems related to oxide degradation are of increasing concern for the development of MOS technology. The 35 leakage current represents one of the most important issues of oxide reliability, especially for MOS applications 36 [6]. The leakage current with temperature can contribute to the thermal runaway of device [7]. Many papers have been devoted to the study of leakage current and its relation with device lifetime [6,8]. Leakage current in a 37 MOSFET can be a significant contributor to power dissipation [9]. A small amount of leakage current is always 38 present, even in healthy devices. The maximum allowable leakage current in a MOSFET is the manufacturer 39 specified zero-gatevoltage drain current (I DSS) and gate body leakage current (I GSS). I DSS is the current 40 flowing between the drain and the source when the gate and source are at the same potential. I GSS is the 41 current flowing between the gate and the source when the source and drain are at the same potential. 42

An electrical stress can produce an increase of the low field leakage current across thin gate oxides, further reducing the lifetime of devices [8]. Failures that are precipitated by excessive leakage currents include junction and dielectric failures [9]. Which consist of leakage through the oxide layer leading to destruction of the dielectric film. Therefore, the leakage current can reach the semiconductor surface and may lead to degradation of the electrical properties of the transistor [9]. It is required to study the hot electron induced performance degradation of MOS transistors. In order to qualify new power RF LDMOS reliability for radar applications, a 3000 h pulsed RF life test has been conducted on a dedicated RF S-band test bench in operating modes [11].

This work presents a degradation study to the properties and various mechanisms of thin gate oxides, based on the electric characterization of leakage current increase on power MOSFET transistor behaviour after new experimental accelerated ageing tests under various conditions. The content of this paper is presented as follows: the section 2 describes the life test bench and the general power RF LDMOS transistor performances. The

54 discussion of simulation and experimental results are shown in Section 3. The conclusion and prospects are given 55 in Section 4.

# <sup>56</sup> 2 II. Experimental Setup Of Ageing Test

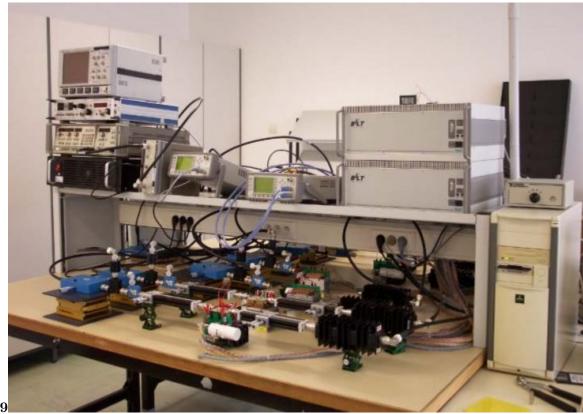

57 Bench And Simulation Process and implemented an innovative reliability bench able to keep track of all RF 58 powers, voltages and device baseplate temperatures whose values correspond to stress operating conditions [14]. 59 This bench is able to keep track many parameters like voltages, currents, base-plate temperature, and peak 60 power. Eight devices is the bench capacity to be tested simultaneously in order to keep it easy to manage. The 61 Fig. ?? and Fig. ?? represent the component under test placed on its test fixture, supplied by DC power and 62 connected to RF connector (type N). The conditions of pulsed RF life test are much closed of radars applications 63 with operating 24h/24h.

The bench consists of three interdependent subsets: \* a microwave part, \* a control/command part piloted by 65 PC, \* thermal module for each devices.

The microwave part essentially allows the power injection and measurement in every branch for each device. Each branch contains a tuner to set precise output VSWR stress on any of the devices. The command/control system ensures the achievement of the following functions: \* biasing voltage supply and current measurement tracking, \* separate control and measurement of each device temperature, \* power switching between the eight devices branches, \* safe data record. \* The measured data on each branch are the following: \* input, output and reflected power, \* output power variation in RF pulse , \* device biasing current, \* temperature.

All data necessary to keep track of each device degradation evolution in real time are secured thanks to the rack. Life-tests are run in the working conditions (pulsed RF) using various device base plate temperatures (10°C, and 150°C) and a high drainsource voltage (44 V) in order to get more power from the device for radar applications.

The RF transistors (8 samples) have been submitted during 3000 hours to ageing test on the reliability bench. This bench operates in radiofrequency pulse mode. During the life test, the goal is to study the component performances in actual working situation to ensure that it will maintain a good performance level. The device under test is placed on a thermal module in order to maintain a constant flange temperature. The command unit manages DC supply voltage, temperature regulation and RF signal monitoring.

The picture of 50?-matched test fixture on thermal support using the Peltier effect for power LDMOS amplifier in S-band radar application.

The component is in centre of support of test specifically designed for operation at full power in pulsed mode (2.9 GHz and 44 V). These values (frequency and tension) are particularly high compared to nominal values given by the manufacturer (2.2 GHz under 26 V). The power RF-LDMOS device under test is a commercial telecom dedicated transistor (encapsulated in a 2-lead flange package with a ceramic cap) S-band operating in class B at saturation and 65 V DC biasing. Indeed, these performances are given in conditions of width pulse 500 ?s with a duty cycle of 50%. The gate length is equal to 0.8µm.

The Power density is equal to 1.89 W/mm. More than 61% of drain efficiency, and a gain More than of 11 dB can be obtained around the S band frequency at 2200 MHz in a common source test circuit. The junction temperature does not exceed 150° C for a flange temperature equal to 65° C. The thermal resistance is 0.2 C/W.

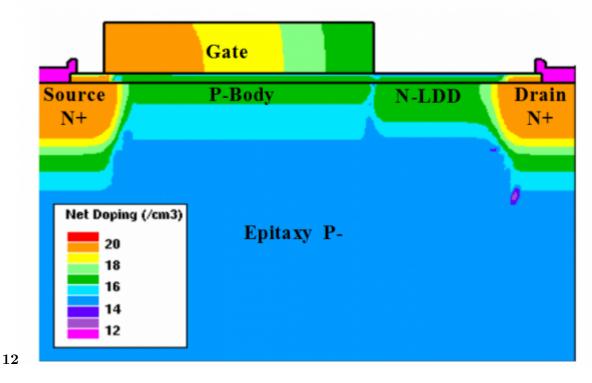

A modified structure of RF power N channel LDMOS, previously developed by Raman et al [15], was implemented and simulated using the physical simulator Atlas of Silvaco [16]. Fig. ?? shows the device's structure with approximate doping wells. The main geometrical and technological parameters are given in Table 1. The implemented structure is typically similar to our tested device. Consequently the qualitative understanding of physical phenomenon will be studied. The suggested structure has a Gaussian doping profile along LDD and channel surface. The doping profile was optimized using a technological process simulation carried out by COURDEDING [16]. Fig. 22

98 SSUPREM3 [16], see Fig. ??.

## 99 **3 III.**

#### 100 4 Results And Discussion

The bench allows to record temperature, currents and voltages (gate and drain), the input power, reflective and output powers. After RF life-tests, the degraded device under test was characterized at ambient temperature, and then a parameter set is extracted.

The current I ds measured is average and in order to have the correct peak current, the duty cycle is needed 104 on the expression of DE. During all the life tests, threshold voltage V th, drain-source current I ds and feedback 105 capacitance C rss are shifted. We can partially conclude that these three DC critical parameters are affected 106 by the RF life test. The increase of the V th was detected and it presented a good correlation with the I ds 107 slump (decrease of the I ds corresponded to increase of the R ds-on). The shift after and before life tests of 108 device threshold voltage V th is presented in fig. ??. An interpretation is proposed to explain the discernable 109 change observed on the feedback capacitance, once Fig. ?? displays changes of S-parameter (S 21 ) before and 110 after RF life-tests at 10°C and 150°C. The gate-source voltage for S-parameters measurement was 4.7 V, and 111 the drain-source voltage was 28 V. The devices are operated in the saturation region. Ideally the I GSS value 112 would be zero for voltage levels that are less than the voltage required to reach the dielectric strength of the gate 113 oxide. In the data sheet the value is less than 40 nA (Table 2). Fig. ??-a shows the gate leakage current (I GSS 114 ) measured of three samples power RF LDMOS before ageing test. 115

Overstressing the gate either periodically with RF or statically with DC can also cause an increase of I GSS 116 and thus degrades device performance with respect to RF power gain. Fig. ??-b shows the increase Gate leakage 117 current (I GSS) measured of three samples power RF LDMOS after ageing test but still far from the total limit of 118 119 device failure. I GSS due to many factors that are related to the integrity of gate oxide and surrounding regions. I GSS can be used to evaluate reliability of this integral component of the MOSFET. Increase of this parameter 120 with a particular device stress can be used to extrapolate the mean time failure (MTTF) of the gate oxide [12]. 121 Other considerations for the gate oxide include careful electrostatic-discharge (ESD) precautions since the gate 122 oxide is easily damaged [12]. 123

A higher junction temperature will increase the leakage current [9,10] which may lead to thermal runaway phenomenon [13]. The electrical parameters are shown in Table 2, in which the measured and the manufacturer's data sheet values of the power MOSFET are compared.

The breakdown voltage as per the manufacturer's data sheet (Vgs=0; I ds =0.2mA) is higher than 75 V. The value of this voltage V (BR)DSS was found 86 V in the case virgin and 81 V after ageing. I DSS include minority carrier injection from the source due to carriers overcoming the energy barrier resulting from surface band bending and also from sub-critical avalanching caused by high electric fields due to a non-ideal body as well as the Laterally-Diffused-Drain (LDD) doping profile [12].

After accelerated RF pulsed life test, the degradation of leakage current can be explained by the increase of V th and C rss. These parameters are degraded due to the interface state generation after stress, device performances should be degraded due to the same degradation mechanism. This indicates that the performance degradation is mainly due to the hot carrier induced interface state generation [17,18]. The Miller capacitance C rss is composed of two parts, the oxide capacitance (C OX ) and the drift region capacitance (C SI ) [19].

The electric parameters of MOS transistor are more and more sensitive to defects bound to the presence of charges in the gate oxide and at the Si/SiO 2 interface [10].

The origin of the observed shift could be related to the presence of very high electric field, which increases carrier injection into the grown silicon dioxide layer (SiO 2) and into interface state Si/SiO 2 [10,19]. The detail of the lateral electric field distribution of the active silicon layer in channel and drift regions is shown in Fig. ??.

The hot carriers produce an additional interface trap density and trapped electron charge which results in a build up of negative charge at Si/SiO 2 interface [20]. This negative charge attracts holes depleting the negative charge in the power LDMOS N-drift region and by consequent increasing the R ds-on device resistance. Hence, R ds-on , C rss and I dsat variations are more remarkable at 10°C, due to the fact that the maximum impact ionization rate is located near the gate edge, see Fig. ??.

The aggressive gate leakage current due to the carrier direct tunneling has become as ultimate limit for gate oxide down scaling [6]. The RF performances are not stable during all 3000 h the life test; we see a variation of I ds . This variation affects the RF performances. According to the literature [19,20], the most probable cause of degradation for power RF LDMOS technology is attributed to hot electron-induced interface state generation and/or impact ionization. May be state interface Si/SiO 2 between drain and gate are responsible of this phenomenon. In order to explain this behaviour, the characterisation of these defects should be investigated. Particularly, the distribution of the data in the figures shows that the aging of the transistor is relatively dependent

154 of the temperature. IV.

#### <sup>155</sup> 5 Conclusions and Prospects

This objective constitutes an investigation to clarify the problems related of Hot Carrier Injection effects for reliability exerted on RF LDMOS under operating conditions of radar application (stress: electrical, thermal and RF). The reliability is shown by monitoring I ds , V th , C rss , S 21 , T°C and I GSS parameters in order to put in evidence the device performances. The simulation approach helps to assess the device robustness under

#### 5 CONCLUSIONS AND PROSPECTS

critical conditions by means of the temperature evaluation, RF and current distributions in LDMOS structures operating. The results obtained highlighted a degradation caused primarily by the mechanism of hot carrier injected in oxide layer and in channel interface states (i.e. hot-electron-induced interface state generation and/or impact ionization), and in turn its effect on critical parameter drifts (I-V, C-V and RF). These are sensitive parameters to the electrons injected in gate/SiO 2 interface traps.

165 This paper represents the starting point for the development of an accurate and more complex FEM based

simulation concept which would correctly include electro-thermal effects. Further failure mechanisms, e.g. the

167 possible activation of the CEM will be integrated within the simulation condition. Moreover, it would be

interesting to make the connection with the normal life of a component, through an aging model or MTTF

(Mean Time To Failure). The comparison of this study with other technologies such as IGBT and VDMOS is underway.

Figure 1: Fig. 1 : Fig. 2 :

170

$<sup>^{1}</sup>$ © 2017 Global Journals Inc. (US)

<sup>&</sup>lt;sup>2</sup>Year 2017 F again more noticeable at 10°C. The C rss at zero drainsource bias is reduced from 2.6pF to 1.8pF at 10 °C, indicating a shift of 30%. Even at 26V bias, the C rss is reduced from 0.43pF to 0.34pF (shift 21%), see fig.5.

$<sup>^3 \</sup>rm Robustness$  Evaluation Study of Power RF LDMOS Devices after Thermal Life Tests © 2017 Global Journals Inc. (US)

### 32017456789

Figure 2: Fig. 3 : 2017 FFig . 4 : Fig. 5 : Fig. 6 : CFig. 7 : Fig. 8 : Fig. 9 :

1

Year 2017 47 of Researches in Engineering ( ) Volume XVII Issue VI Version I F Global Journal

Figure 3: Table 1 :

# $\mathbf{2}$

| Parameter            |                    | Value (µm    | ı)          |                  |

|----------------------|--------------------|--------------|-------------|------------------|

| Source length        |                    |              | 1.1         |                  |

| Source-gate spacing  |                    |              | 1           |                  |

| Gate length          |                    |              | 0.8         |                  |

| Gate-drain spacing   |                    |              | 3           |                  |

| Drain length         |                    |              | 1.1         |                  |

| Gate oxide thickness |                    |              | 0.065       |                  |

| Parameter measured   | Measured value Deg | raded Virgin | n shift%    | Data sheet value |

| I GSS                | 12 pA              | 340 pA       |             | ? 40 nA          |

|                      | -                  | >100         |             |                  |

| I DSS                | 2 nA               | 90 nA        |             | ? 1.5 μA         |

|                      |                    | >100         |             |                  |

| V th                 | 4.1 V              | 4.83 V       | $17 \ 4v$ ? | ; ? 5v           |

| V (BR)DSS            | 86 V               | 81 V         | 6           | 75V ?            |

| Crss                 | 0.43pF 0.34 pF 21  |              |             | typ. 0.5 pF      |

| S 21                 | -7.3 dB -10 dB 36  |              |             | ? 11 dB          |

|                      |                    |              |             |                  |

Figure 4: Table 2 :

- [Latry and Dherbécourt ()] A 5000 h RF life test on 330 W RF-LDMOS transistors for radars applications, O

Latry , P Dherbécourt . 2010. p. .

- [Raychaudhuri ()] 'A simple method to qualify the LDD structure against the early mode of hotcarrier

degradation'. A Raychaudhuri . *IEEE Trans. Electron Devices* 1996. p. .

- [Atlas User's Manual-Device Simulation Software Silvaco International ()] 'Atlas User's Manual-Device Simulation Software'. Silvaco International, (Santa Clara, California) 1998.

- [Yuan and Jiang ()] 'Evaluation of hotelectron effect on LDMOS device and circuit performances'. Jiann-Shiun

Yuan , L Jiang . *IEEE Trans Electron Dev* 2008. p. .

- [Takagi et al. ()] 'Experimental evidence of inelastic tunnelling in stress-induced leakage current'. S Takagi , N

Yasuda , A Toriumi . *IEEE Trans Electron Dev* 1999. 46 p. .

- [Gares et al. ()] 'Hot carrier reliability of RF N-LDMOS for S band radar application'. M Gares , M Masmoudi

P Bertram , J Marcon , M Belaid . M. Reliability 2006. 46 p. .

- [Liu ()] 'Hot-Carrier-Induced Linear Drain Current Degradation of LDMOS Under Pulse Gate Stress With

Amplitudes'. S Liu . E. Devi. Letter 2013. p. .

- [Starkov ()] 'Local oxide capacitance as crucial parameter for characterization of hot-carrier degradation in n MOSFETs'. I Starkov . Journal Vacuum Science Technology B 2013. p. .

- [Corso ()] Measurement of the hot carrier damage profile in LDMOS devices stressed at high drain voltage. Micro.

Reliability, D Corso . 2007. p. .

- 189 [Li and Schram ()] Mechanism of O 2 -anneal induced Vfb shifts of Ru gated stacks, Z Li, T Schram. 2007. p. .

- [Mohammed Aftab Alam ()] 'Member Influence of Molding Compound on Leakage Current in MOS Transistors'.

Mohammed Aftab Alam . *IEEE Trans on components* 2011. p. .

- [Ielmini A and Sottocornola ()] Modeling of stress-induced leakage current and impact ionization in MOS devices,

Daniele Ielmini A , Alessandro Sottocornola , S . 2002. p. .

- [Dibra et al. ()] 'On the Origin of Thermal Runaway in a Trench Power MOSFET'. Donald Dibra , Matthias

Stecher , Stefan Decker . *IEEE Trans Electron Dev* 2011. 58 p. .

- [Kerber et al. ()] 'Origin of the threshold voltage instability in SiO2 /HfO2 dual layer gate dielectrics'. A Kerber

, E Cartier , L Pantisano , R Degraeve . *IEEE Electron Dev Lett* 2003. p. .

- [John and Hanson ()] Relate LDMOS device parameters to RF performance. STMicroelectronics, Application note: AN 1228, P John, B Hanson. 2000.

- [Aritome et al.] 'Reliability issues of flash memory cells'. S Aritome, R Shirota, G Hemink. Proc IEEE 1993,

(IEEE 1993) p. .

- 202 [Shuming et al. ()] 'RF LDMOS with extreme low parasitic feedback capacitance and high hot-carrier immunity'.

- 203 X Shuming , F Pangdow , W Jianqing , Changhong .  $I\!E~D\!M$  1999. p. .

- [Reggiani et al. ()] 'Simulation of Hot-Carrier and Thermal Degradation in STI-LDMOS Transistors, Electron

Devices'. S Reggiani , G Barone , Tcad . *IEEE Transactions* 2013. p. .

- [Raman et al. ()] 'Simulation of nonequilibrium thermal effects in power LDMOS transistors'. D G Raman , T

S Walker , Fisher . Solid-State Electronics 2003. p. .

- [Reggiani and Barone ()] 'TCAD Smulation of Hot-Carrier and Thermal Degradation in STI-LDMOS Transis tors'. S Reggiani , Barone . *IEEE Transactions Electron Devices* 2013. p. .