Artificial Intelligence formulated this projection for compatibility purposes from the original article published at Global Journals. However, this technology is currently in beta. *Therefore, kindly ignore odd layouts, missed formulae, text, tables, or figures.*

## Low Power Conditional Sum Adder using Modified Ripple Carry Adder

Anjana R.<sup>1</sup>, Anjana R.<sup>2</sup> and Vicky Kanoji<sup>3</sup>

<sup>1</sup> Laxmi institute of Technology

Received: 15 December 2013 Accepted: 5 January 2014 Published: 15 January 2014

#### 7 Abstract

- <sup>8</sup> Carry select adder (CSeLA) is mainly used to alleviate the propagation delay caused by carry

- $_{9}\;$  bit and upon which sum bit is generated. It produces n+1 sum from n bits. In this Paper, a

- <sup>10</sup> simple Gate level implementation of regular Carry Select Adder is compared with our

- <sup>11</sup> proposed work. Based on the comparison made in terms of power, delay and area, it is found

- 12 that there is considerable reduction in area and power with delay overhead. Both regular and

- <sup>13</sup> proposed methods are modeled using 180nm CMOS technology. From the results obtained, it

- <sup>14</sup> is clear that proposed CSeLA is better than regular CSeLA.

15

3

5

16 Index terms— CMOS, delay efficient, CSeLA, low power, Propagation delay.

### 17 **1 INTRODUCTION**

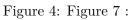

esigning power efficient, high performance adder is one of the major concerns as far as VLSI Sub system is considered. Speed is usually limited due carry propagation bit of an adder. The sum of final bit is generated by the carry propagation from the previous bit to next stage. The CSeLA consists of two multiplexed ripple carry adder and performs operation in parallel with carry Cin=0 and Cin=1, then final sum is selected through multiplexer (mux). Due to multiplexed RCA, there is considerable increase in area, which reveals that there is scope for reduction in area [2].

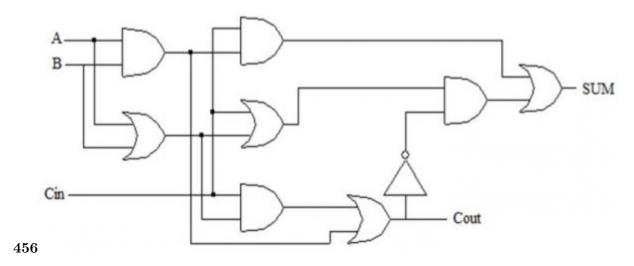

The main idea behind this work is to compare regular carry select adder with modified carry select adder. The modified carry select adder uses Boolean function based RCA along with modified XOR gate. The main advantage of this modified RCA comes with reduced gate count than the n-bit Full adder circuit.

This paper is organized as follows. Section II deals with the delay and area measurement of conventional full adder. Section III explains the Boolean function based RCA design. Section IV shows the comparison between proposed methods with regular CSeLA. Section V shows the power and delay evaluation of regular CSeLA and modified CSeLA. The implementation method and results obtained are analyzed in Section VI. The work is finally concluded in Section VII.

Author ?: Research Scholar, Deeksha Integrated, Bharathiar University, India. e-mail: anjana.lit@lvs.co.in Author ?: UG Student, Laxmi Institute of Tech, Sarigam, Gujarat, India. e-mail: vickykanoji@gmail.com Author ?: Department of Electronics Engineering, MANIT, Bhopal, India. e-mail: asomkumar@gmail.com II.

# <sup>35</sup> 2 DELAY AND AREA EVALUATION OF CONVENTIONAL <sup>36</sup> ADDER

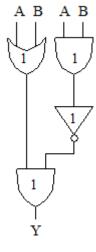

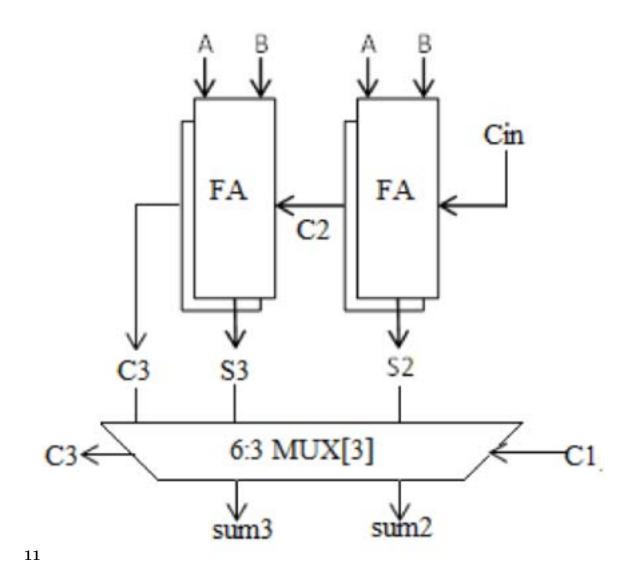

The XOR gate is implemented using conventional AOI logic. The delay and area is found from this AOI logic, with the assumption that each gate having delay equal to one and the gate with the longest path contribute critical path delay. The total number of gate in AOI logic contributes to total area of logic block. Based on this method, 2:1 Mux, full adder, half adder, XOR are evaluated. The main idea is to use modified RCA instead of RCA with Cin=0 to reduce area and power consumption of regular CSeLA. The AOI implementation of full adder requires 14 gates, while the modified full adder CSeLA has two ripple carry adder with Cin=0 and Cin=1

- and multiplexer to choose data one among them. One of two RCA is replaced with Boolean function (BF), which

- 44 has reduced number of gate count. From the truth table of full adder its evident that sum is obtained from D

- 45 ? The group 2 has two bit RCA, which comprises 1 FA and 1 HA with Cin=0 and other RCA with Cin=1 is 46 replaced with modified BEC -1.

<sup>47</sup> 3 Delay and area evaluation of CSeLA

<sup>48</sup> ? Based on the delay and area analysis listed in Table ??, the total number of gate count for group 2 is ? <sup>49</sup> Propagation delay of proposed carry select adder is given as, T Proposed = T s + (N-1) T mux + T sum = 3ns<sup>50</sup> ? Area and delay is computed in same way as that of group 2 and listed in Table 1.

51

V.

## 52 4 Experimental Results

The proposed work is designed using DSCH simulator and synthesized using 180nm technology. The synthesized verilognetlist is imported to Microwind and automatic layout is generated. From Microwind, power, area and delay is found by choosing different technology.

Table 2 shows the simulation results of both regular and modified CSeLA in terms of delay, power and area. Each individual cell in the design contributes the total cell area. Total power consumption is the sum of leakage power, switching power and static power. Area, power, delay, power delay product (PDP) is shown in fig. in

terms of percentage reduction. The total power reduction for 8-b, 16-b, 32-b are 9.3 %, 23.1%, 9.7% respectively.

60 Similarly Percentage reduction in area is shown in fig. There is delay overhead of 14.9%, 12.1%, 6.18% respectively.

## 61 5 Conclusion

- 62 A modified approach for carry select adder is proposed in this paper to reduce power and delay compared to

- $^{63}$  conventional CSLA. The modified structure of RCA and BEC provides the scope for further area reduction and

- 64 power for 90nm technology. From the experimental results it is clear that there is 9.3 %, 23.1%, 9.7% reduction 65 in power and 10.5 %, 24.9%, 18.3% reduction in area with 14.9%, 12.1%, 6.18% delay overhead. The modified

- Carry Save Adder is thus area and power efficient. 12

Figure 1: Figure 1 :

66

$<sup>^{1}</sup>$ © 2014 Global Journals Inc. (US)

$<sup>^2 \</sup>odot$  2014 Global Journals Inc. (US) Low Power Conditional Sum Adder Using Modified Ripple Carry Adder

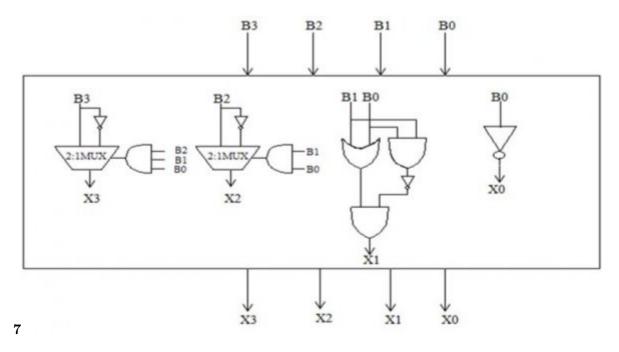

Figure 3: Figure 4 : Figure 5 : Figure 6 :

Figure 5:

Figure 6: Figure 11 :

1

| 1-Bit Adder<br>Full adder Half adder 2:1 | $6\ 3\ 3\ 3$ |   | Issue V Version I<br>( ) F Volume XIV          |

|------------------------------------------|--------------|---|------------------------------------------------|

| MUX XOR AND                              | 1            | 1 | of Researches in Engineering<br>Global Journal |

Figure 7: Table 1 :

#### 5 CONCLUSION

## $\mathbf{2}$

| Word<br>Size | Adder             | Power<br>(mW) | Area(um 2) | Delay(ns) | PDP(pW) |

|--------------|-------------------|---------------|------------|-----------|---------|

| 8-Bit        | Conventional CSLA | 0.32          | 941        | 1.61      | 0.515   |

|              | Modified CSLA     | 0.29          | 842        | 1.85      | 0.3885  |

| 16-Bit       | Conventional CSLA | 0.69          | 2435       | 2.62      | 1.80    |

|              | Modified CSLA     | 0.53          | 1829       | 2.94      | 1.55    |

| 32-Bit       | Conventional CSLA | 0.92          | 4683       | 4.93      | 4.53    |

|              | Modified CSLA     | 0.83          | 3826       | 5.13      | 4.25    |

| VI.          |                   |               |            |           |         |

Figure 8: Table 2 :

#### <sup>67</sup> .1 This page is intentionally left blank

- 68 [Bedrij ()], O J Bedrij. Carry-Select Adder, IRE Trans. Electron. Comput 1962. p. .

- [Kim and Kim (2001)] '64-Bit Carry-Select Adder With Reduced Area'. Y Kim , L.-S Kim . *Electron. Lett* May 2001. 37 (10) p. .

- <sup>71</sup> [He et al. ()] 'An Area Efficient 64-Bit Square Root Carry-Select Adder For Lowpower Applications'. Y He , C

<sup>72</sup> H Chang , J Gu . *Proc. IEEE Int. Symp. Circuits Syst*, (IEEE Int. Symp. Circuits Syst) 2005. 4 p. .

- [Ramkumar et al. ()] 'ASIC Implementation Of Modified Faster Carry Save Adder'. B Ramkumar , H M Kittur

, P M Kannan . *Eur. J. Sci. Res* 2010. 42 (1) p. .

- <sup>75</sup> [Ceiang and Hsiao] 'Carry-Select Adder Using Single Ripple Carry Adder'. T Y Ceiang , M J Hsiao . *Electron.* <sup>76</sup> Lett

- <sup>77</sup> [Rabaey ()] Digtal Integrated Circuits-A Design Perspective, J M Rabaey . 2001. Upper Saddle River, NJ:

<sup>78</sup> Prentice-Hall.

- 79 [Ramkumar et al. (2012)] 'Low-Power And Area-Efficient Carry Select Adder'. B Ramkumar , M Harish , Kittur

- 80 . Global Journal of Researches in Engineering February 2012. 20 (2) . (IEEE transaction on VLSI Systems)