Artificial Intelligence formulated this projection for compatibility purposes from the original article published at Global Journals. However, this technology is currently in beta. *Therefore, kindly ignore odd layouts, missed formulae, text, tables, or figures.*

# Novel Design of BCD to Excess-3 Code Converter in Quantum Dots Cellular Automata (QCA) Ali Bahar<sup>1</sup> <sup>1</sup> Mawlana Bhashani Science and Technology University *Received: 12 December 2013 Accepted: 3 January 2014 Published: 15 January 2014*

## 7 Abstract

Quantum-dot cellular automata (QCA) represent a new technology at the nanotechnology 8 level. Conventional digital technologies use ranges of voltage or current to represent binary 9 values. In contrast, QCA uses the positions of electrons in quantum dots to represent binary 10 Values '0' and '1'. Quantum technology has gradually applied in various fields. A 11 quantum-dot cellular automaton is projected as a promising nanotechnology for future ICs. A 12 QCA is an array of structures known as quantum-dots. The advantages of using QCA 13 technology are smaller circuit size, higher clock frequency, and lower power consumption. Two 14 electrons occupy each cell. Each electron is free to tunnel between dots within one cell, but 15 cannot leave the cell. The two electrons within each cell repel each other to diagonally 16 opposite corners of the cell. This leaves only two stable states for each cell. These two states 17 are used to represent logic values. The occupation of upper-left and lower-right dots represent 18 logic '0'. In this case, the QCA cell is said to be polarized to -1. Similarly, the occupation of 19 upper-right and lower left dots represent logic '1'. In this case, the QCA cell is said to be 20 polarized to +1. In this paper, a BCD to excess-3 code converter circuit is proposed based on 21 QCA logic gates: the 3-input MV OR gate, 3-input MV AND gate, MV NOT gate. This 22 3-input AND 3-input OR gates, 3-input complex gates, multi-input complex gates. The 23 proposed circuit is a remising future in constructing of nano-scale low power consumption 24 information processing system and can stimulate higher digital applications in QCA. 25

26

Index terms— quantum cellular automata (QCA); QCA logic gates; BCD-to-excess-3 code converter in

QCA; 3-input QCA and gate, BCD by QCA.

# <sup>29</sup> 1 Introduction

uantum technology has gradually applied in various fields [1,2]. Quantum-dot cellular automata are projected as

a promising nanotechnology for future ICs [3,4]. A QCA is an array of structures known as quantum-dots.

Computing with QCA is achieved by the tunneling of individual electrons among the quantum-dots inside

individual electrons among the quantum-dots inside a cell and the classical columbic interaction among them.

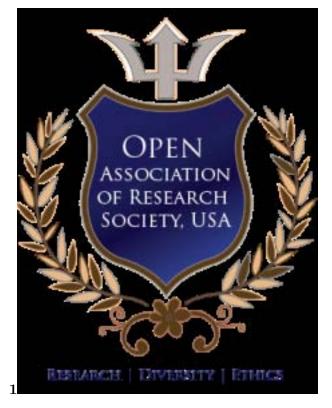

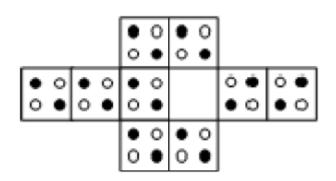

Author ? ? ? ?: Department of Information and Communication Technology, Mawlana Bhashani Science and Technology University, Tangail, Bangladesh. e-mail: bahar\_mitdu@yahoo.com A quantum cell can be viewed as a set of four charge containers or dots positioned at the corners of a square, as shown in Fig. 1. It contains two extra mobile electrons. The electrons can quantum mechanically tunnel between dots but cannot come out from the cell and are forced to settle at the corner positions due to coulomb interaction. Thus, there exist two equivalent energetically minimal arrangements for the electrons in a QCA cell (Figure 1), a QCA cell and its binary Logic are shown, the energetically position of the diagonal electrons identifies the binary logic 0 or 1. This

41 phenomenon is useful in nanotechnology which affects high resolution fast electronic circuits. The QCA cells

#### 5 SIMULATION RESULT AND DISCUSSION

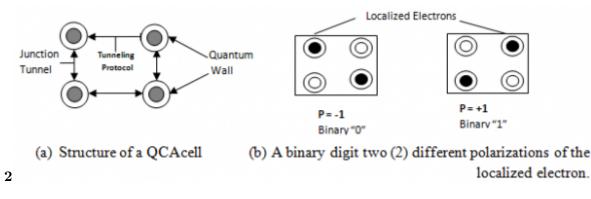

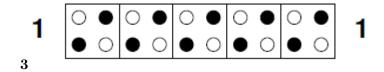

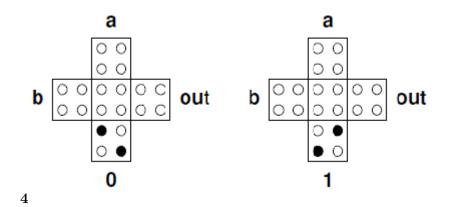

themselves comprise the interconnecting wires as described in [4]. An example of a QCA wire is shown in Figure 2. In this example, a value of 1 is transmitted along the wire. Only a slight polarization in a cell is required to fully polarize its neighbor. The direction for the flow of information through a gate or a wire is controlled by a four stage clocking system described in [4] which raises and lowers barriers between the cells. Described in [3] were other logic gates formed by restricting the polarity of one input to the 3-input majority gate to be a constant value. Figure 3 illustrates a 2-input AND gate and a 2-input OR gate formed in this manner. By replacing input c with a cell having a fixed

# <sup>49</sup> 2 Proposed Circuit and Presentation a) BCD-to-EXCESS-3 <sup>50</sup> code converter

A conversion circuit must be inserted between the two systems if each uses different codes for the same information. 51 Thus, a code converter is a circuit that makes the two systems compatible even though each uses a different 52 binary code. To convert from binary code A to binary code B, the input lines must supply the bit combination 53 of elements as specified by code A and the output lines must generated the corresponding bit combination of 54 code B. A combinational circuit performs this transformation by means of logic gate. The design procedure of 55 code converters will be illustrated by means of a specific example of conversion from the BCD to the excess-3 56 code. The bit combinations for the BCD and excess-3 code [5] listed in Table 1. Since each code uses four bits 57 to represent a decimal digit, there must be four input variables and four output variables. Let us designate the 58 four input binary variables by the symbols A,B,C and D and the four output variables by the W,X,Y and Z. The 59 truth table relating the input and output variables is shown in Table 2. The bit combinations for the inputs and 60 their corresponding outputs are obtain directly from Table 1. We note that four binary variables may have 16bit 61 combinations, only 10 of which are listed in the truth table. The six bit combinations not listed for the input 62 variables are don't-care combinations. Since they will never occur, we are liberty to assign to the output variables 63 either a 1 or a 0, whichever gives a similar circuit. The manipulation of BCD-to-excess code converter, shown 64 below, illustrates the flexibility obtain with multiple-output systems when implemented with three or more levels 65 of gates. 66

# <sup>67</sup> 3 Z = D, Y = CD + (C+D), Z = B'(C+D) + B(C+D), W = A + B(C+D)<sup>68</sup> B(C+D)

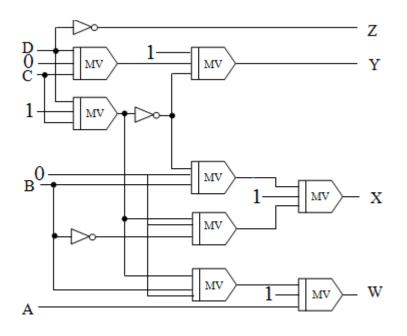

The block diagram of QCA is the BCD-toexcess-3 code converter gate shown in Fig. 5. The BCDto-excess-3 72 code converter gate has four inputs and four outputs asshown in figure 5. Uses eight majority voter (MV) gate 73 and two NOT gate to design BCD-toexcess-3 code converter in QCA as shown in Figure 5. The fundamental logic 74 gate for QCA is the BCD-toexcess-3 code converter gate shown in Figure ?? that is composed of two hundred 75 (200) cells with total area of 0.06 ?m2. Four of these, representing the inputs to the cell, are labeled A, B, C and 76 D. using the terminology of [3]. The center cell is the "device cell" that performs the calculation for three input 77 majority voter gates in QCA. The remaining cell, labeled out, provides the output. The circuit shown in Figure 78 ?? 79

#### 80 4 Methods

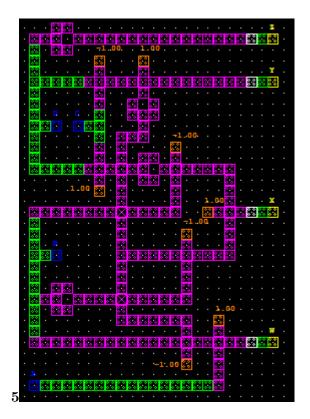

First of all, the logic behind any proposed circuit is deduced and then the circuit diagram is drawn at gate level. 81 The gate level circuit is converted to QCA layout using majority gates, inverters, etc. as described in the above 82 sections and then these designs are simulated in QCA Designer which is the product of an ongoing research effort 83 by the Walus Group at the University of British Columbia to create a design and simulation tool for QCA. The 84 designer tool allows the designer to layout a QCA design and simulates it quickly. QCA Designer has provided a 85 new platform for developers; results from simulations, using this tool, have been published by many international 86 groups ??6][7][8] ??9][10][11]. Results obtained by this tool are then compared to theoretical values to verify the 87 correctness of the circuit. 88

89 IV.

# <sup>90</sup> 5 Simulation Result and Discussion

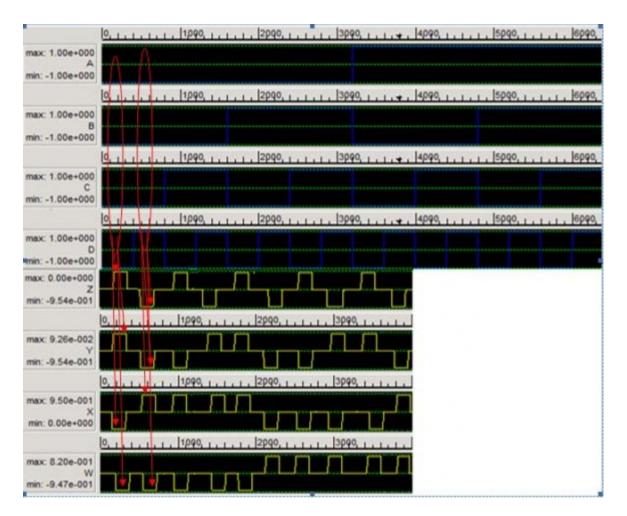

The circuit was functionally simulated using the QCA Designer. We can find the Output value of W, X, Y, Z is two level such as low and high when the various input digits of A,B,C,D. We look into the every output values of W, X, Y, Z are translating the input data successfully. Based on the mentioned reversible logic gate BCD-to-excess-3 code converter gate numeral logical circuit design method, we also construct BCD-to-excess-3 code converter gate by QCA. The sizes of layouts are measured on the basis of size of QCA cells. The All designs are carefully clocked and were functionally verified using QCADesigner; a layout and simulation tool for QCA. Finally, in Table ??, designs are compared according to number of cells, area, and delay. Table ?? : Result

analysis of proposed BCD-to-excess-3 code converter gate in QCA V.

# 99 6 Conclusion

100 This paper present a BCD-to-excess-3 code converter gate based on QCA does logic gates .This QCA circuit

- design provide a new functional paradigm for information encoding. In addition, QCA binary logic functions and

- the associated new nano-technology will provide high-speed computing, high-density applications. It is believed

- that QCA will become a more practical ways to create a faster and denser circuit

Figure 1: Figure 1 :

Figure 2: Figure 2 :

103

<sup>&</sup>lt;sup>1</sup>Year 2014 © 2014 Global Journals Inc. (US)

$<sup>^2 \</sup>odot$  2014 Global Journals Inc. (US) Novel Design of BCD to Excess-3 Code Converter in Quantum Dots Cellular Automata (QCA)

<sup>&</sup>lt;sup>3</sup>Year 2014 © 2014 Global Journals Inc. (US) Y = CD + (C+D)

Figure 3: Figure 3 :

Figure 4: Figure 4 :

Figure 5: Novel

Figure 6:

Figure 7: Figure 5 :

## 6 CONCLUSION

Figure 8:

$\mathbf{1}$

Figure 9: Table 1 :

Figure 10: Table 2 :

- 104 [Global Journal of Researches in Engineering], Global Journal of Researches in Engineering

- $[Maj] , = Maj . (Maj\{(0)', 0, Maj(0, 1, 1), 1, Maj\{0, 0, Maj(0, 1, 1)'\}] = Maj[Maj\{1, 0, 1\}, 1, Maj\{0, 0, (1)'\})$

- 106 [W=A+B], W=A+B.  $(C+D) =Maj[A,1,Maj\{B,0,Maj(C,1,D)\})$

- 107 [Global Journal of Researches in Engineering], Global Journal of Researches in Engineering

- 108 [Mostafarahimi et al. ()] 'A novel design for quantum-dot cellular automata cells and full adders'. A Mosta-109 farahimi , O Kavehei , K Navi . J Appl Sci 2012. 7 p. .

- [Li and Li ()] 'A Quantum Immune Evolutionary Algorithm and Its Application'. H Li , S Li . Journal of

Computational Information Systems 2011. 7 (8) p. .

- 113 [Townsend and Abraham (2004)] 'Complex gate implementations for quantum dot cellular automata'. W J

- 114 Townsend, J A Abraham. *Proc. 4th IEEE Conference Nanotechnology*, (4th IEEE Conference Nanotechnol-115 ogvPacific Grove) 16-19 August 2004. p. .

- 116 [Orlov et al. ()] 'Experimental demonstration of clocked single-electron switching in quantum-dot cellular au-

- $^{117}$ tomata'. A Orlov , A Islamshah , Kummamuru , R<br/>k , R Ramasubramaniam , G Toth , Lent , C<br/>s , G H

- 118 Bernstein , Snider , Gl . Appl Phys Lett 2000. 77 (2) p. .

- <sup>119</sup> [Walus and Schulhof (2004)] 'GA: High level exploration of quantum-dot cellular automata (QCA)'. K Walus ,

- G Schulhof , Jullien . Conf. Rec. 38 th Asilomar Conf. Signals, Systems and Computers, (Pacific Grove)

November 2004. p. 3033.

- [Lent and Tougaw (1993)] 'Lines of interacting quantum-dot cells: A binary wire'. C S Lent , P D Tougaw .

Journal of Applied Physics November 15. 1993. 74 (10) p. 6227.

- 124 [Liu ()] Yi Liu . Modified Quantum Genetic Algorithm Apply for Flow Shop Scheduling Problem, 2008. 4 p. .

- [Novel Design of BCD to Excess-3 Code Converter in Quantum Dots Cellular Automata (QCA)] Novel Design of BCD to Excess-3 Code Converter in Quantum Dots Cellular Automata (QCA),

- [Lent et al. ()] 'Quantum Cellular Automata: The physics of computing with quantum dot molecules'. C S Lent

, P D Tougaw , W Prod . *Physics and Computation* 1994. p. .

- [Kumar et al. (2009)] 'SP: A robust pulsed flip-flop and its use in enhanced scan design'. R Kumar , Bollapalli ,

Kc , R Garg , T Soni , Khatri . *IEEE* 2009. October 2009. p. .

- 131 [Morris Mano; Walus and Jullien (2003)] 'V: Computer arithmetic structures for quantum cellular automata'.

- M Morris Mano ; Walus , K Jullien , G , Dimitrow . Conference Record of the Thirty-Seventh Asilomar

- Conference on Signals, Systems and Computers, November 2003. p. 12. professor of Engineering, California

State University, Los Angeles, (Pacific Grove)